FSMC总结

总结 FSMC 外设的使用方法和原理。

0 基础知识

FSMC:Flexible Static Memory Controller的缩写,译为灵活的静态存储控制器。它可以用于驱动包括SRAM、NOR FLASH以及NAND FLSAH类型的存储器,不能驱动如SDRAM这种动态的存储器。它的不足在于不可以驱动动态存储器。但是如果具有FMC这个外设,则可以支持控制SDRAM存储器。

由于fsmc是映射在stm32内存中的,所以其和sram、falsh、eeprom等等外设不一样,其可以直接对数据进行操作,而不需要什么先发送写或读信号,发送什么地址信号等等。

所有的外部存储器共享控制器输出的地址、数据和控制信号,每个外部设备可以通过一个唯一的片选信号加以区分。FSMC在任一时刻只访问一个外部设备。

具有静态存储器接口的器件包括:

- 静态随机存储器(SRAM)

- 只读存储器(ROM)

- NOR闪存

- PSRAM(4个存储器块)

1.0 详细结构

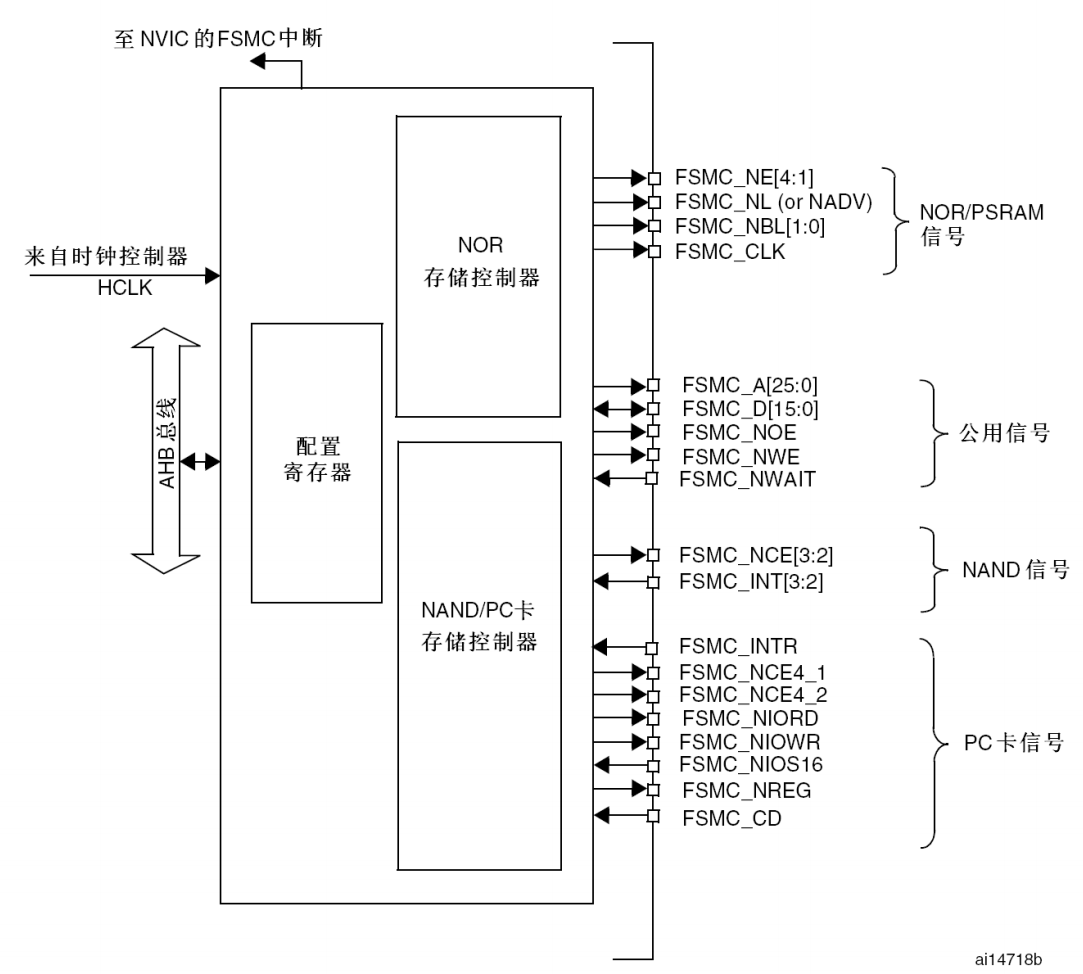

由上可知,FSMC主要有四个部分:

- AHB

- NOR闪存控制器

- NAND闪存、PC卡控制器

- 外部接口

下面一一说明每个部分的作用。

1.1 AHB接口

AHB接口为内部CPU和其它总线控制设备访问外部静态存储器提供了通道。

AHB操作被转换到外部设备的操作。当选择的外部存储器的数据通道是16或8位时,在AHB上的32位数据会被分割成连续的16或8位的操作。

AHB时钟(HCLK)是FSMC的参考时钟。

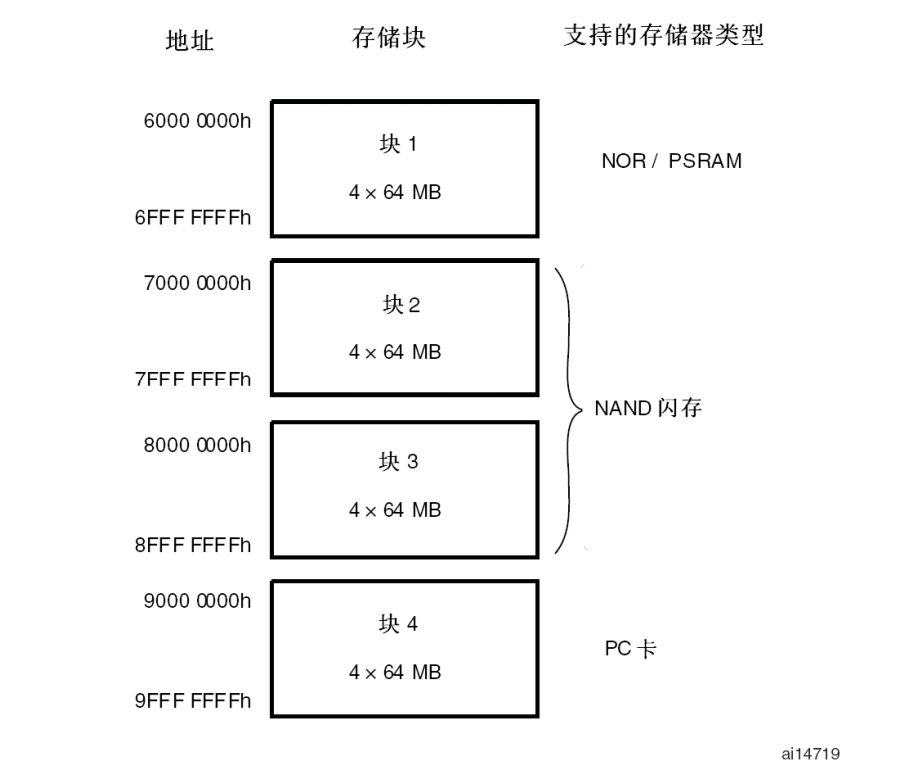

2.0 外部设备地址映像

从FSMC的角度看,可以把外部存储器划分为固定大小为256M字节的四个存储块:

同时这四个内存块中的每一个又被细分。

具体的划分可以在stm32参考手册中查找到。19.4节

3.0 NOR闪存和PSRAM控制器

上面我们知道这个FSMC,被划分为四个部分的内存。但是其实只有三种存储器类型。

FSMC可以产生适当的信号时序,驱动下述类型的存储器:

- 异步SRAM和ROM

- 8位

- 16位

- 32位

- PSRAM(Cellular RAM)

- 异步模式

- 突发模式

- NOR闪存

- 异步模式或突发模式

- 复用模式或非复用模式

FSMC对每个存储块输出一个唯一的片选信号NE[4:1],所有其它的(地址、数据和控制)信号则是共享的。

3.1 控制寄存器

3.2 时序寄存器

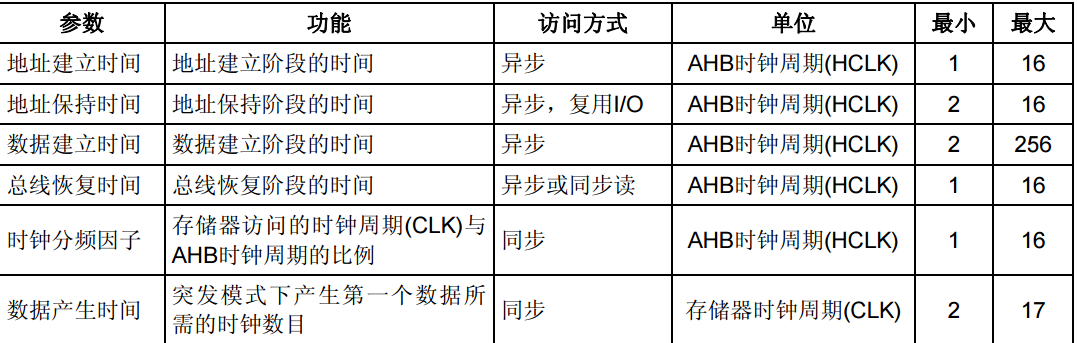

由于每一种的存储设备具有不同的读写时序, 所以FSMC提供了多种时序模式来匹配对应的存储设备的读写时序.

时序寄存器主要控制的是这个设备的时钟信号.

- 所有信号由内部时钟HCLK保持同步,但该时钟不会输出到存储器;

- FSMC始终在片选信号NE失效前对数据线采样,这样能够保证符合存储器的数据保持时序(片选失效至数据失效的间隔,通常最小为0ns);

- 当设置了扩展模式,可以在读和写时混合使用模式A、B、C和D(例如,允许以模式A进行读,而以模式B进行写)。

这张表主要显示了时序寄存器中的内容.

FSMC外设支持输出多种不同的时序以便于控制不同的存储器, NOR闪存和PSRAM支持了6中模式:

- 模式一, SRAM/CRAM

- 模式A, 只是模式一的OE反向

- 模式B(模式二), NOR闪存

- 模式C, 只是模式B的OE反向

- 模式D, 带地址扩展的异步操作

- 复用模式, 地址/数据复用的NOR闪存异步操作

每一类存储设备需要使用对应的模式

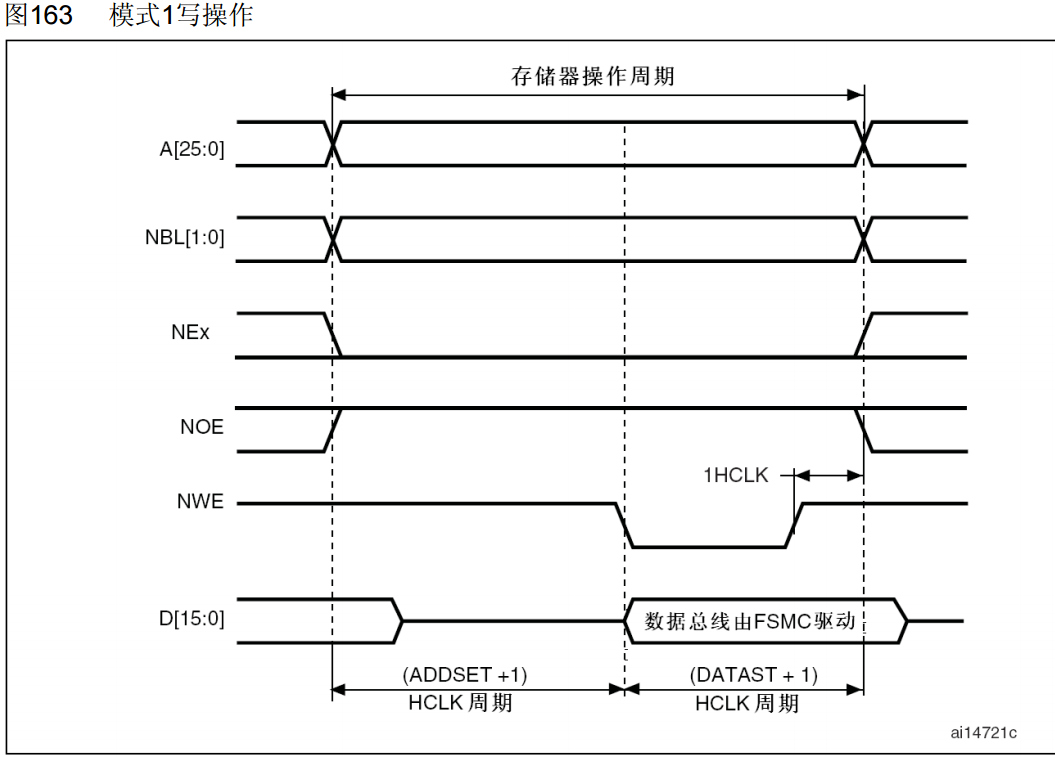

每一种模式的时序都不相同,例如在模式一下的读时序和写时序如下:

图中的N代表的是低位有效

其余模式可以去官方的参考手册中查找(19.5.4).

4.0 编程

以上我们知道FSMC支持三类存储设备,并且这三类存储器又支持者好几种不同的模式。我们编程主要是控制时序寄存器和控制寄存器。

由于FSMC支持了三大类存储设备, 所以就是其有好几种不同的时序结构体和控制结构体.

比如说NOR flash存储器的时序结构体定义如下:

1 | |

需要注意的是, FSMC中的时钟设置的单位是HCLK周期数,并且可以是0-0xF个周期数.按STM32标准库的默认配置,HCLK的时钟频率为168MHz,即一个HCLK周期为1/168 us。